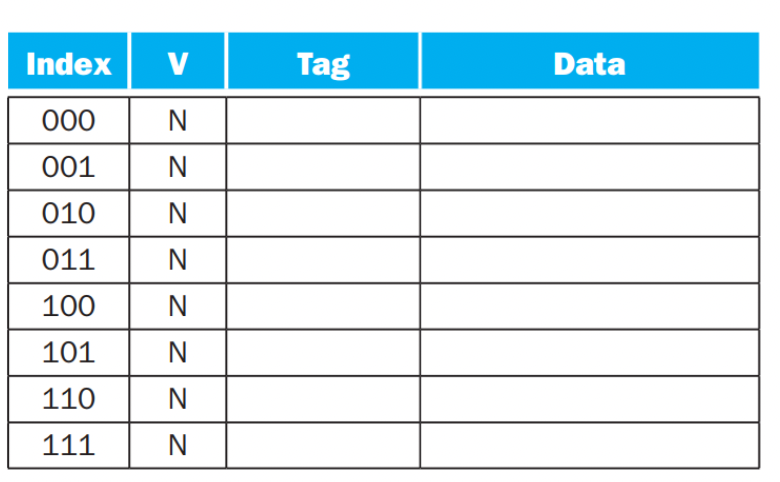

캐시의 각 entry에는 index + valid bit + tag + data로 구성된다.

캐시에는 8개의 entry가 있고, 각각 3bit의 index를 기반으로 식별된다.

1bit의 V에는 entry의 정보가 valid한지 여부를 나타낸다.

데이터가 해당 엔트리에 배치되면 해당 데이터를 지칭하기 위해 2bit의 tag가 설정된다.

처음에는 캐시가 비어있기에, 처음의 모든 valid bit는 N으로 설정된다. 태그와 데이터도 비어있다.

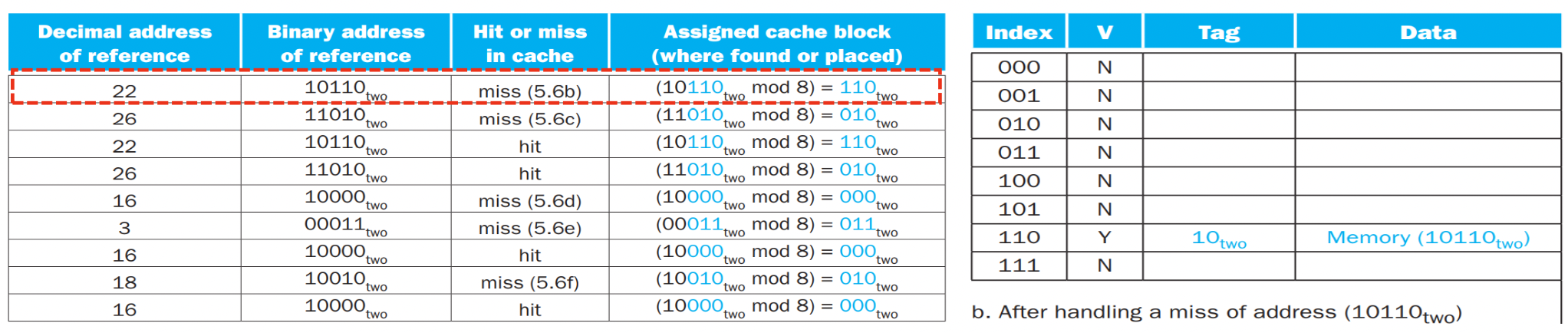

참조된 데이터에 캐시가 있는 경우, hit가 발생하고 데이터는 캐시로부터 제공된다.

없는 경우엔 miss가 발생하고 기존 데이터는 메인메모리에서 복사된, 참조된 데이터로 대체된다.

만약 데이터 10110(2)이 요청되면 index가 110인 캐시 블록에 배치될 것이다.

이 때 110의 valid bit은 N이므로 miss이다.

데이터 10110(2)는 메인메모리에서 가져와 index가 110인 캐시 블록에 저장된다.

태그는 10으로 설정되고, valid bit은 Y로 설정된다.

여기서 만약 10110(2)이 다시 한번 요청되면, 110의 valid bit은 Y이고, tag가 10이므로 hit이다.

최근에 참조된 데이터 항목이 이전에 참조된 데이터 항목을 대체하는데, 이 동작은 캐시가 시간적 지역성을 활용할 수 있도록 한다.

'학교강의필기장 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조[22]: associative cache (0) | 2023.06.22 |

|---|---|

| 컴퓨터구조[21]: Direct Mapped Cache for the Real World (0) | 2023.06.22 |

| 컴퓨터구조[19]: memory, Direct Mapped Cache (0) | 2023.06.22 |

| 컴퓨터구조[18]: Data Hazard - Stall (0) | 2023.06.22 |

| 컴퓨터구조[17]: Data Hazard - Data Forwarding (0) | 2023.06.22 |

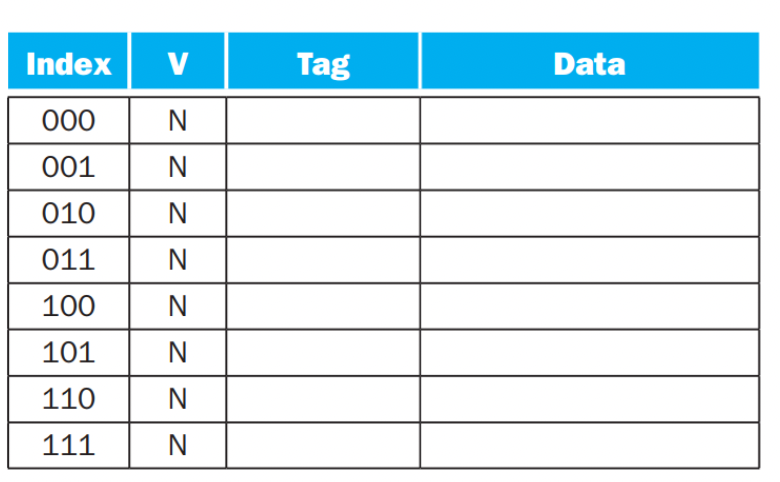

캐시의 각 entry에는 index + valid bit + tag + data로 구성된다.

캐시에는 8개의 entry가 있고, 각각 3bit의 index를 기반으로 식별된다.

1bit의 V에는 entry의 정보가 valid한지 여부를 나타낸다.

데이터가 해당 엔트리에 배치되면 해당 데이터를 지칭하기 위해 2bit의 tag가 설정된다.

처음에는 캐시가 비어있기에, 처음의 모든 valid bit는 N으로 설정된다. 태그와 데이터도 비어있다.

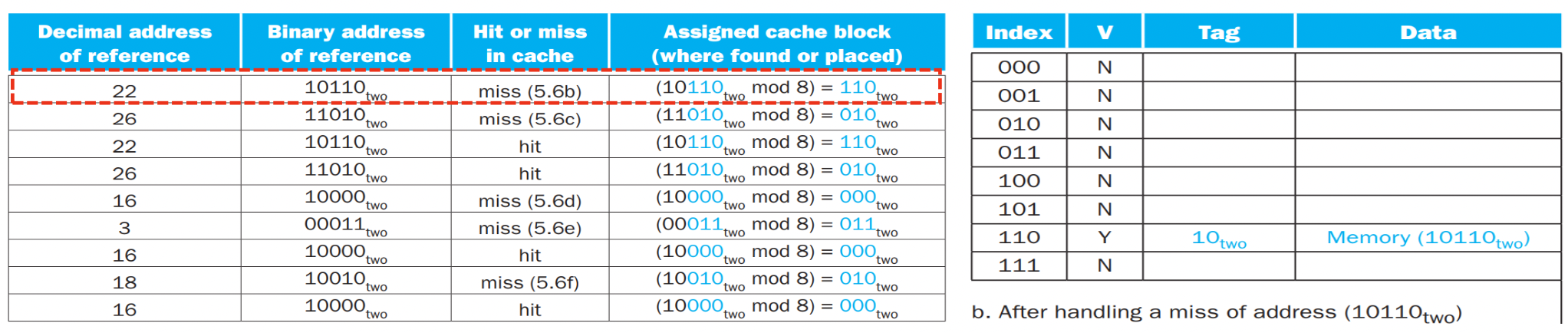

참조된 데이터에 캐시가 있는 경우, hit가 발생하고 데이터는 캐시로부터 제공된다.

없는 경우엔 miss가 발생하고 기존 데이터는 메인메모리에서 복사된, 참조된 데이터로 대체된다.

만약 데이터 10110(2)이 요청되면 index가 110인 캐시 블록에 배치될 것이다.

이 때 110의 valid bit은 N이므로 miss이다.

데이터 10110(2)는 메인메모리에서 가져와 index가 110인 캐시 블록에 저장된다.

태그는 10으로 설정되고, valid bit은 Y로 설정된다.

여기서 만약 10110(2)이 다시 한번 요청되면, 110의 valid bit은 Y이고, tag가 10이므로 hit이다.

최근에 참조된 데이터 항목이 이전에 참조된 데이터 항목을 대체하는데, 이 동작은 캐시가 시간적 지역성을 활용할 수 있도록 한다.

'학교강의필기장 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조[22]: associative cache (0) | 2023.06.22 |

|---|---|

| 컴퓨터구조[21]: Direct Mapped Cache for the Real World (0) | 2023.06.22 |

| 컴퓨터구조[19]: memory, Direct Mapped Cache (0) | 2023.06.22 |

| 컴퓨터구조[18]: Data Hazard - Stall (0) | 2023.06.22 |

| 컴퓨터구조[17]: Data Hazard - Data Forwarding (0) | 2023.06.22 |