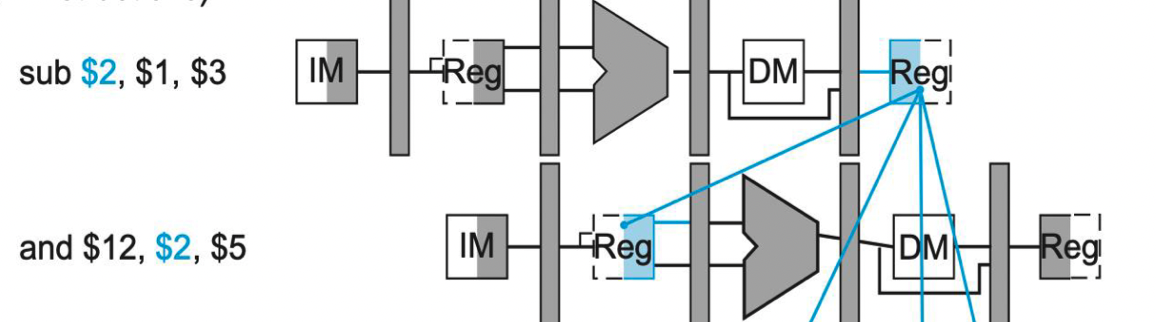

만약 아래와 같은 명령어가 실행됐다고 가정하자.

sub $2, $1, $3

and $12, $2, $5

이 때, $1 - $3 값이 -20이라 할 때, and 연산에서 $2는 -20을 기대하지만 아직 sub 연산이 끝나지 않았으므로 10을 가져온다.

이 문제를 Data Hazard 라고 한다.

이를 위한 해결책으로 Data Forwarding을 사용할 수 있다.

sub 명령의 EX/MEM 레지스터 값을 and 연산의 Rs 포트로 보낼 수 있다.

즉, 다른 명령의 레지스터를 ALU의 소스로 사용하는 것이다.

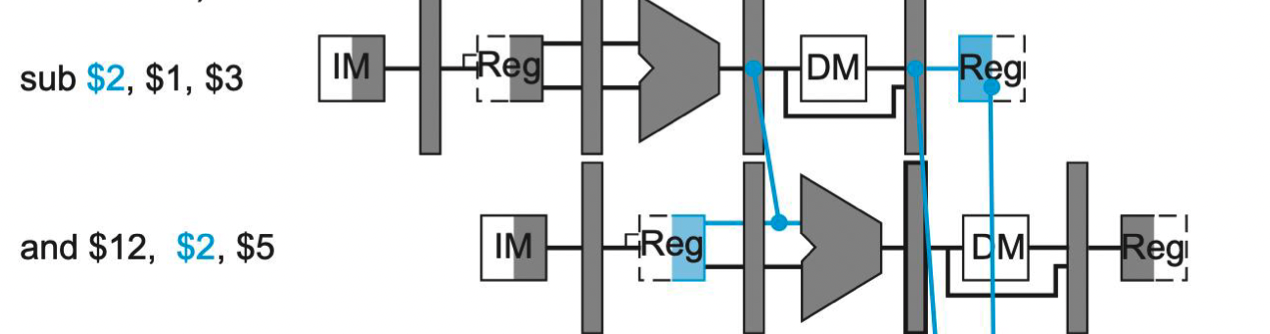

datapath는 data hazard를 감지할 수 있어야 한다.

즉, destination register가 source register로 사용되는지 확인해야 한다.

여기서 and 연산의 경우, sub 연산의 EX/MEM.RegisterRd 와 and 연산의 ID/EX.RegsterRs 값이 같은지 확인한다.

여기서 or 연산의 경우, sub 연산의 MEM/RB.RegisterRd 와 or 연산의 ID/EX.RegsterRt 값이 같은지 확인한다.

정리하자면, data hazard가 발생하는 4가지 케이스가 있다.

- EX/MEM.RegisterRd = ID/EX.RegisterRs - 첫 번째 명령어와 두 번째 명령어 사이

- EX/MEM.RegisterRd = ID/EX.RegisiterRt - 첫 번째 명령어와 두 번째 명령어 사이

- MEM/WB.RegisterRd = ID/EX.RegisterRs - 첫 번째 명령어와 세 번째 명령어 사이

- MEM/WB.RegisterRd = ID/EX.RegisterRt - 첫 번째 명령어와 세 번째 명령어 사이

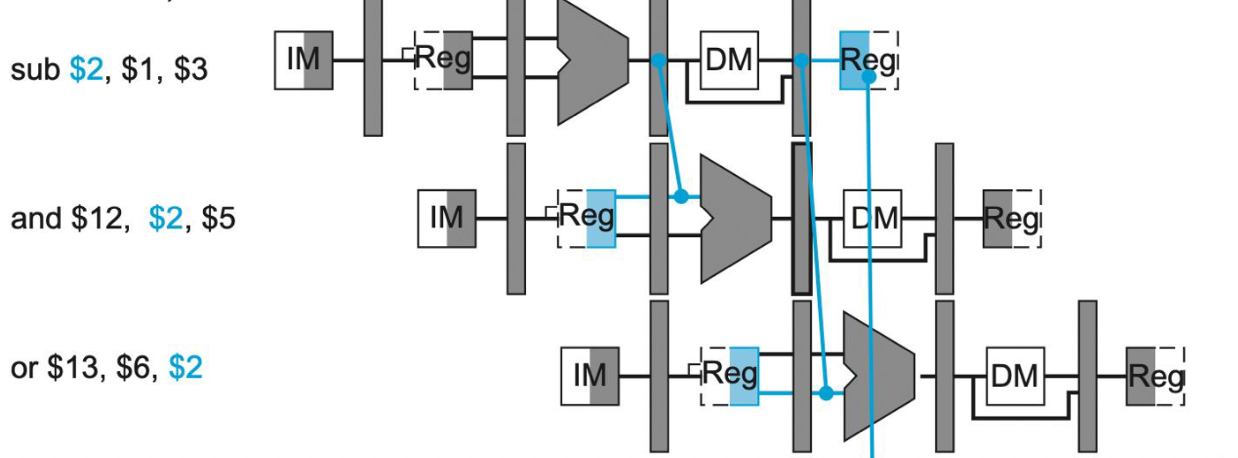

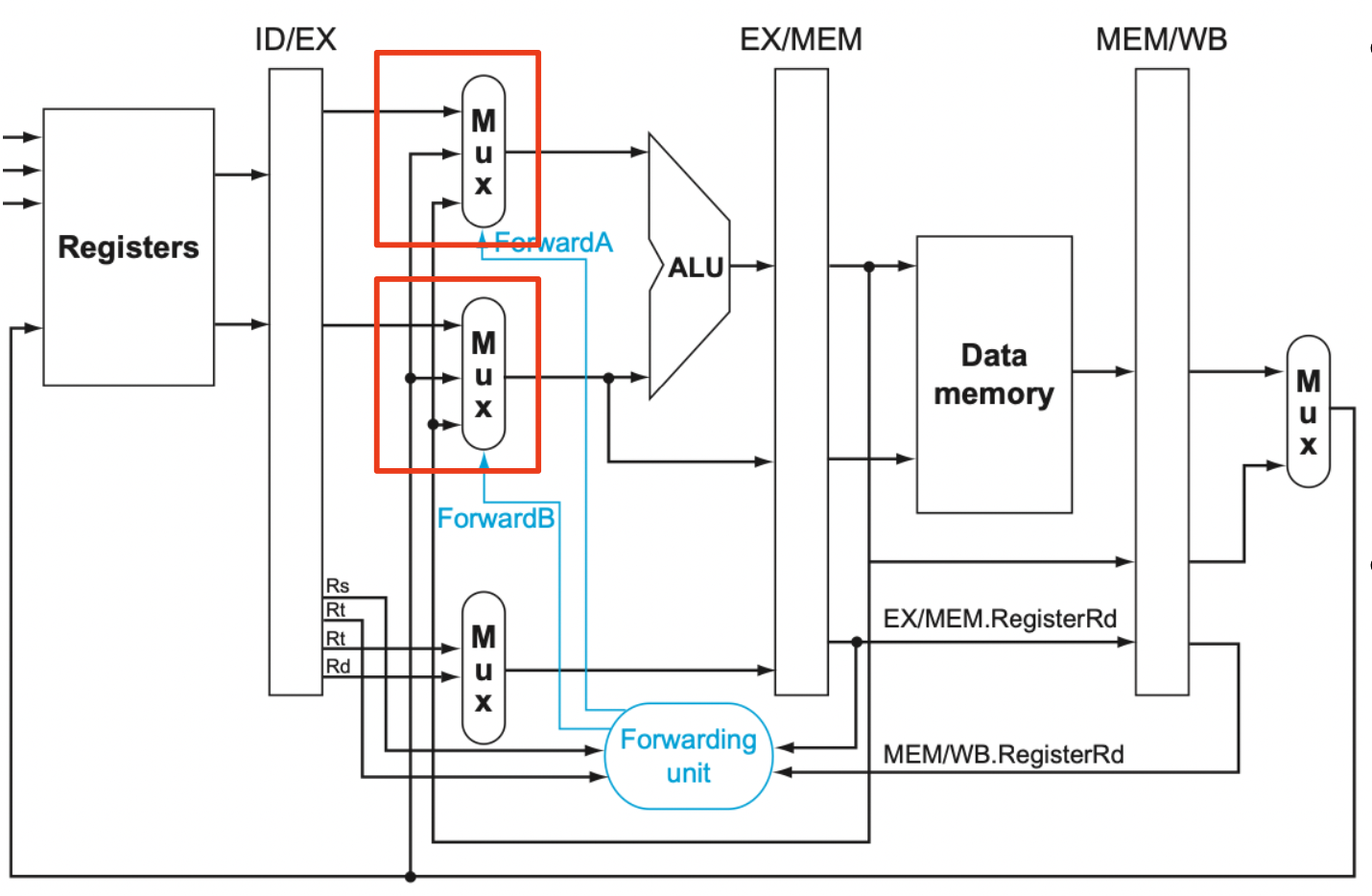

data forwarding을 수행하기 위해, data hazard를 감지하기 위한 네 가지 입력을 사용하는 forwarding unit을 배치한다.

또 ALU의 두 소스에 대해 multiplexer를 배치한다.

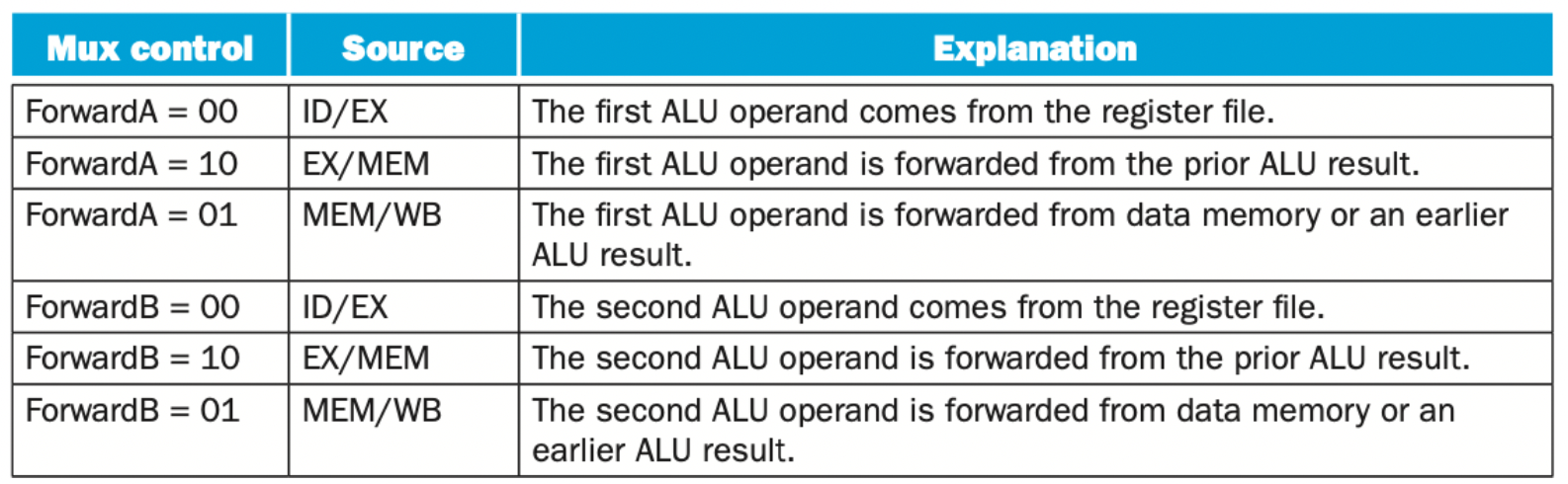

multiplexer의 입력은 다음과 같다.

1) 레지스터 파일(ID/EX)에서의 값 => 데이터 하자드가 없을 때

2) 데이터 메모리 또는 이전 ALU 결과(MEM/WB)에서의 값

3) 이전 ALU 결과(EX/MEM)에서의 값

forwarding unit은 2비트 신호를 사용해서 이 세 가지 입력 중 하나를 결정한다.

- 첫 번째 ALU 소스에 대한 forwardA

- 두 번째 ALU 소스에 대한 forwardB

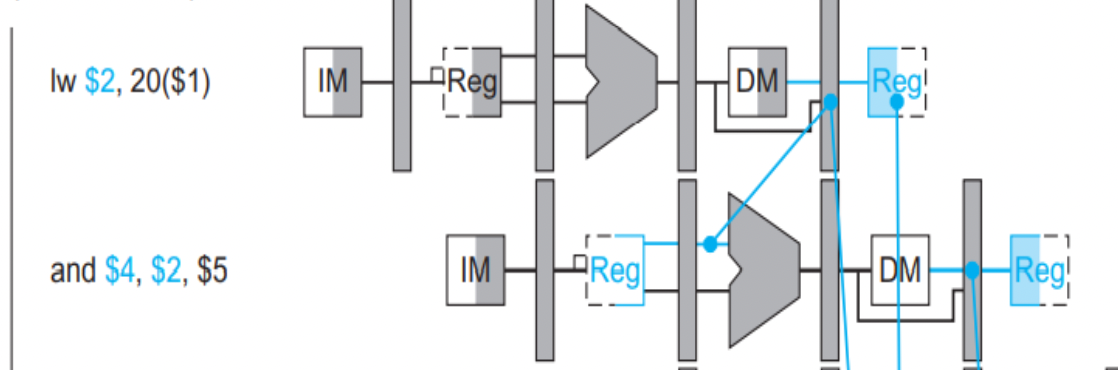

하지만, data forwarding으로도 data hazard를 해결할 수 없는 경우도 있다.

lw 명령어가 register에 $2를 기록하는 시간은 CC5이고, and 명령어가 ALU 연산을 수행하는건 CC4이다.

data forwarding이 MEM/WB 레지스터에서 ALU의 Rs 포트로 포워딩 할 때는 이미 늦었다.

'학교강의필기장 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조[19]: memory, Direct Mapped Cache (0) | 2023.06.22 |

|---|---|

| 컴퓨터구조[18]: Data Hazard - Stall (0) | 2023.06.22 |

| 컴퓨터구조[16]: control signals for pipelined datapath (0) | 2023.06.22 |

| 컴퓨터구조[15]: pipelined - lw, sw, bugfix (0) | 2023.06.22 |

| 컴퓨터구조[14]: Pipelining (0) | 2023.06.22 |