How to Locate a Block in the Cache?

- direct mapping cache에서는 index를 찾고, index의 valid bit와 tag를 확인한다.

- set associative cache에서는 set을 찾고, 해당 set 내의 모든 블록에 대해 valid bit와 tag를 확인한다.

N-way associtaive cache에서는 set 내의 n개의 블록을 비교해야 한다.

예를 들어, 1024개의 1word block으로 구성된 4-way set associative cache는, 1 word block의 byte offset에 2bit, 1024/4 (256=2^8)에 8bit, tag에는 22bit를 할당한다.

만약 miss가 발생한다면, 요청한 데이터 블록이 캐시에 존재하지 않는다.

요청된 데이터 블록은 메인 메모리에서 가져와 set에 저장한다.

요청된 블록을 set에 저장하기 위해 기존의 블록 중 하나를 캐시에서 교체해야 한다.

set 내의 기존 4개의 블록 중 하나를 선택해서 교체해야 한다.

가장 일반적으로 사용되는 방법은 가장 최근에 사용되지 않은 (least-recently-used, LRU) 블록을 선택하는 것이다.

교체되는 블록은 가장 오랫동안 사용되지 않은 블록이다.

이는 시간적 지역성(temmporal locality)을 향상시킬 수 있기에 의미가 있다.

가상메모리

또 다른 두 개의 계층 메모리 시스템인, 메인메모리 - 보조저장장치 간의 관계를 살펴보자.

- 모든 애플리케이션의 data set은 storage에 저장된다.

- 메인 메모리는 storage의 일부 data set을 보유한다. (subset)

- CPU는 메인 메모리가 모든 data set을 보유하고 있는 것처럼 느껴서 가상메모리라 부른다.

- page : 가상 메모리의 기본 단위이다. 캐시의 블록과 대조된다.

- page fault : virtual memory miss.

DRAM은 장치 주소를 사용해서 액세스할 수 있는데, 이를 physical addresses라고 한다.

하지만 CPU는 physical addresses 대신 virtual addresses 를 사용한다.

load/store/branch/jump 에서 생성되는 메모리 주소는 virtual addresses이다.

이는 애플리케이션의 모든 데이터가 DRAM의 제한된 용량에 수용될 수 없기 때문이다.

사실 CPU에서 실행중인 애플리케이션은 일부 데이터를 메인 메모리에 갖고 있고, 나머지 데이터를 storage에 가지고 있지만 CPU는 이를 신경쓰지 않고 애플리케이션의 가상 주소를 사용한다.

메인 메모리에서 데이터를 요청하기 위해 address translation이 필요하다.

- 프로세서는 virtual addresses로 data set을 요청한다.

- DRAM은 physical addresses를 사용해서 액세스를 한다.

애플리케이션의 데이터는 메인메모리나 storage 중 어느 한 곳에 있을 수 있다.

- 데이터가 메인메모리에 있는 경우, virtual address -> physical address로 변환된다.

- 데이터가 storage에 있는 경우, virtual address -> disk address로 변환된다.

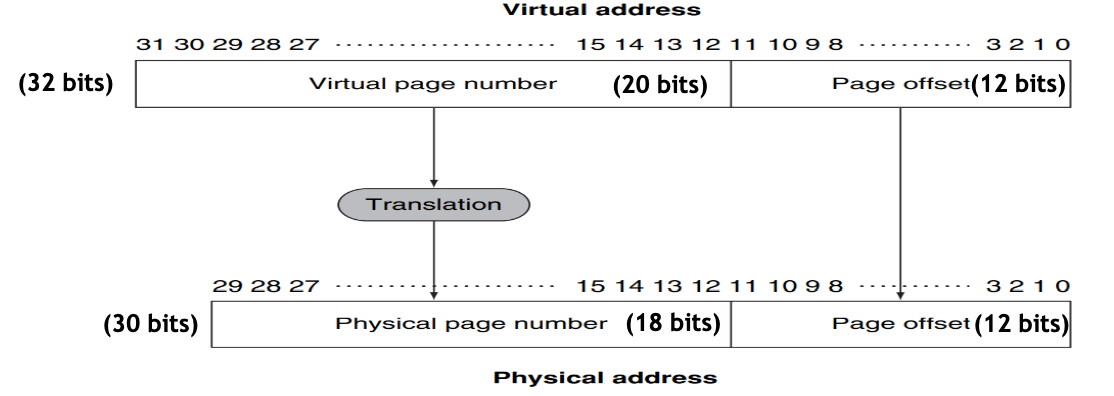

페이지의 virtual address는 virtual page number + page offset으로 나눌 수 있다.

page offset은 페이지 내의 특정 byte를 나타낸다.

따라서 page offset에 할당된 비트 수로부터 페이지의 크기를 추론할 수 있다.

여기서, 32bit address의 하위 12bit가 page offset으로 사용되며, 페이지의 크기는 212byte(4KB)이다.

virtual address의 상위 부분은 virtual page number를 나타낸다.

address translation : virtual page number -> physical page number

page offset은 변경되지 않으며, page 내의 byte를 지정하는데 사용된다.

일반적으로, virtual page 의 수는 physical page의 수보다 훨씬 크다.

여기서 physical address의 bit로 부터 DRAM의 크기를 추론할 수 있다.

physical page number는 30bit이므로, 2^30 bit = 1GB 의 메모리를 가진다.

이 1GB DRAM에는 212byte (2^12) byte의 2^18개의 page가 존재한다.

'학교강의필기장 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조[24]: Page table, TLB (0) | 2023.06.22 |

|---|---|

| 컴퓨터구조[22]: associative cache (0) | 2023.06.22 |

| 컴퓨터구조[21]: Direct Mapped Cache for the Real World (0) | 2023.06.22 |

| 컴퓨터구조[20]: Access a Direct Mapped Cache (0) | 2023.06.22 |

| 컴퓨터구조[19]: memory, Direct Mapped Cache (0) | 2023.06.22 |