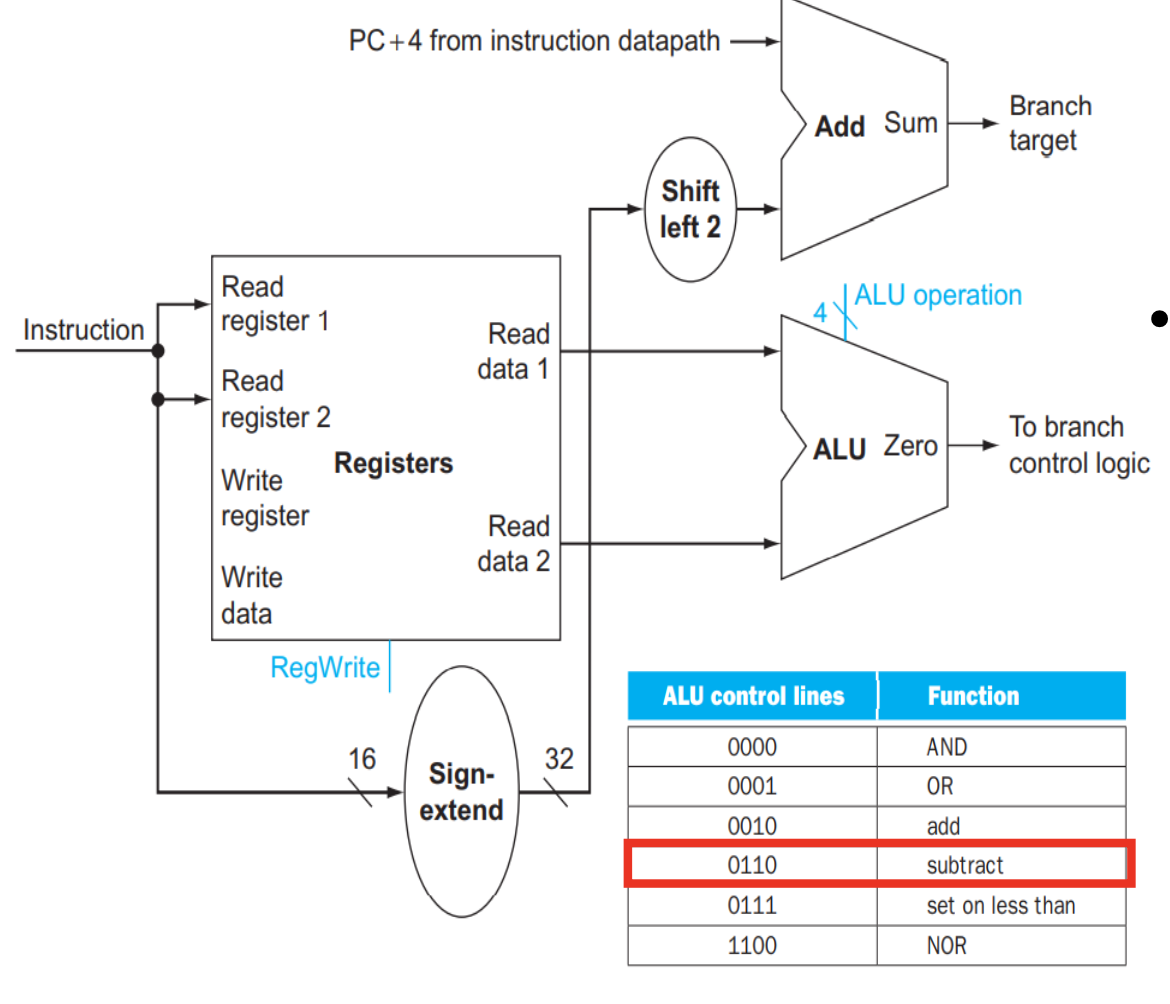

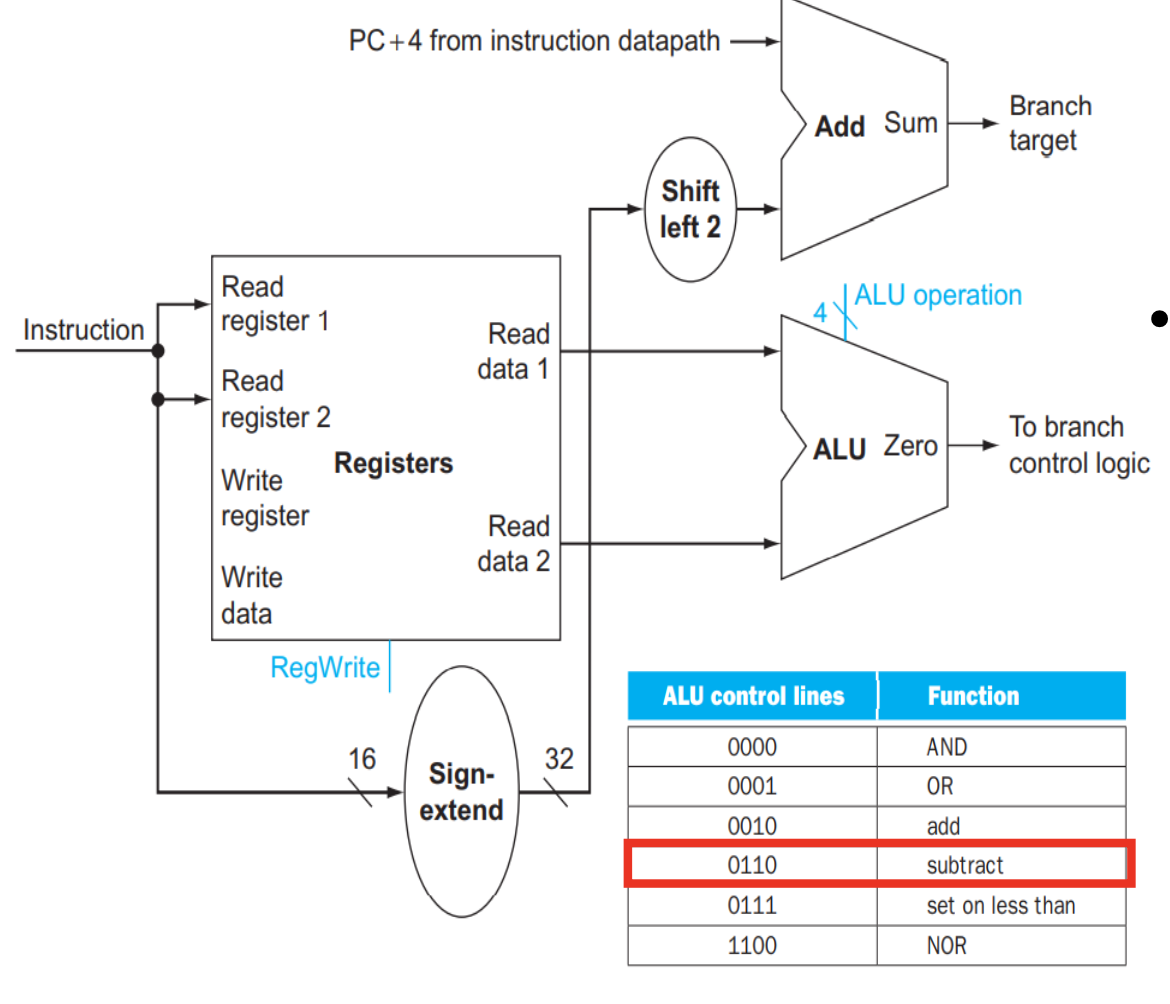

위 회로는 브랜치 분기 명령어에서 사용되는 회로다. 이는 두 가지 출력으로 나뉘는데, 예를 들어 beq $t1 8($t2)가 입력됐다고 가정하자.

첫번째 출력은 대상 주소 출력이다. 상대 주소인 8은 Sign-extend 회로로 16bit에서 32bit로 변환된다. 그 후 Shift left 2 회로로 4가 곱해져 워드 단위의 상대 주소가 된다. Adder(가산기)로써 PC+4와 합쳐져 대상 주소가 출력된다.

두번째 출력은 조건문에 따른 출력이다. Read register에 $t1과 $t2가 입력되고, Read data로 출력된다. 출력된 값은 ALU에 입력되어 subtract 연산을 수행한다. 만약 zero flag가 활성화된다면 둘은 같은 것이므로 대상 주소에 위치한 명령어가 수행된다.

1) instruction을 fetch하기 위해선 PC, Instruction memory, Adder가 필요하다.

2) R-type instruction을 실행하기 위해서는 register file과 ALU가 필요하다.

3) lw/sw instruction를 실행하기 위해서는 register file과 ALU, Sign Extension Unit, Data memory가 필요하다.

4) branch instruction을 실행하기 위해서는 register file, ALU, Sign Extension Unit, Shift left 2, Adder가 필요하다.

위 회로에 beq $t1 3($t2) 가 입력됐다고 가정하자 (PC의 출력이 beq $t1 3($t2)인 것이다.)

우선, PC는 출력했으므로 현재 명령어 위치를 Adder의 입력으로 받아 4가 더해진 값이 PCSrc와 연결된 Mux의 0번째 자리에 들어간다. 또, 추후 offset_value와 더해질 Adder의 입력으로 들어간다.

그리고 offset_value인 3은 Sign Extension Unit로 32bit로 변환되고 Shift left 2 회로로 4가 곱해진 뒤 Adder의 입력으로 들어간다. 그렇게 PC+4와 offset_value*4는 더해져 대상주소가 되고, 이는 PCSrc와 연결된 Mux의 1번째 자리에 들어간다.

$t1과 $t2는 Registers의 입력으로 들어가고, 그의 데이터가 출력된다. 출력된 데이터는 ALU의 입력으로 들어가고, subtract 연산을 수행한다. 이때 Zero flag가 활성화되면 둘은 같은 것이므로 PCSrc는 1이 되고 PC에는 대상 주소가 입력된다.

활성화되지 않는다면 branch가 실패한 것이므로 PCSrc가 0이 되어 PC에는 PC+4가 입력된다.

'학교강의필기장 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조[13]: Control Unit, Jump (0) | 2023.04.16 |

|---|---|

| 컴퓨터구조[12]: ALU Control Unit, Signal 정리 (0) | 2023.04.12 |

| 컴퓨터구조[10]: Datapath, Datapath Elements (0) | 2023.04.09 |

| 컴퓨터구조[9]: MIPS 구조 요약 (0) | 2023.04.09 |

| 컴퓨터구조[8]: address mode - PC-relative / Pseudo-direct (0) | 2023.04.09 |

위 회로는 브랜치 분기 명령어에서 사용되는 회로다. 이는 두 가지 출력으로 나뉘는데, 예를 들어 beq $t1 8($t2)가 입력됐다고 가정하자.

첫번째 출력은 대상 주소 출력이다. 상대 주소인 8은 Sign-extend 회로로 16bit에서 32bit로 변환된다. 그 후 Shift left 2 회로로 4가 곱해져 워드 단위의 상대 주소가 된다. Adder(가산기)로써 PC+4와 합쳐져 대상 주소가 출력된다.

두번째 출력은 조건문에 따른 출력이다. Read register에 $t1과 $t2가 입력되고, Read data로 출력된다. 출력된 값은 ALU에 입력되어 subtract 연산을 수행한다. 만약 zero flag가 활성화된다면 둘은 같은 것이므로 대상 주소에 위치한 명령어가 수행된다.

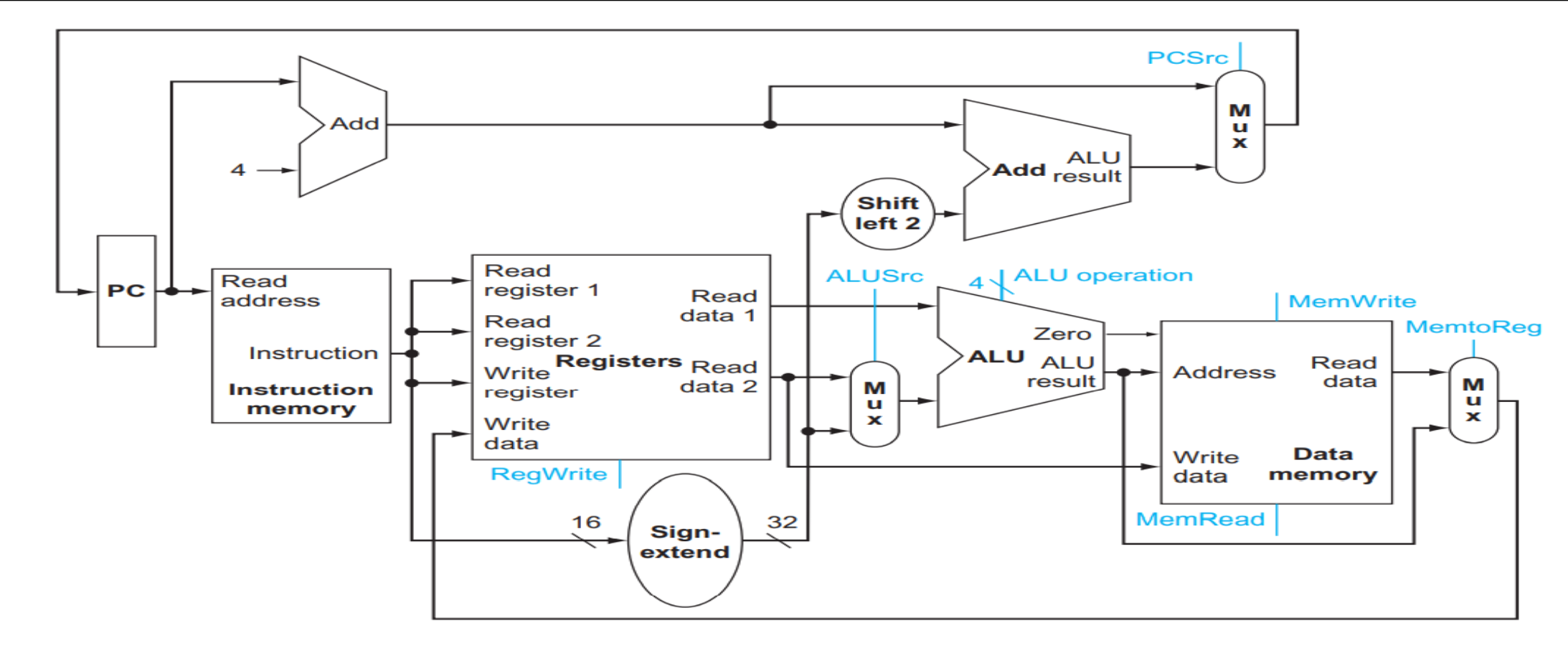

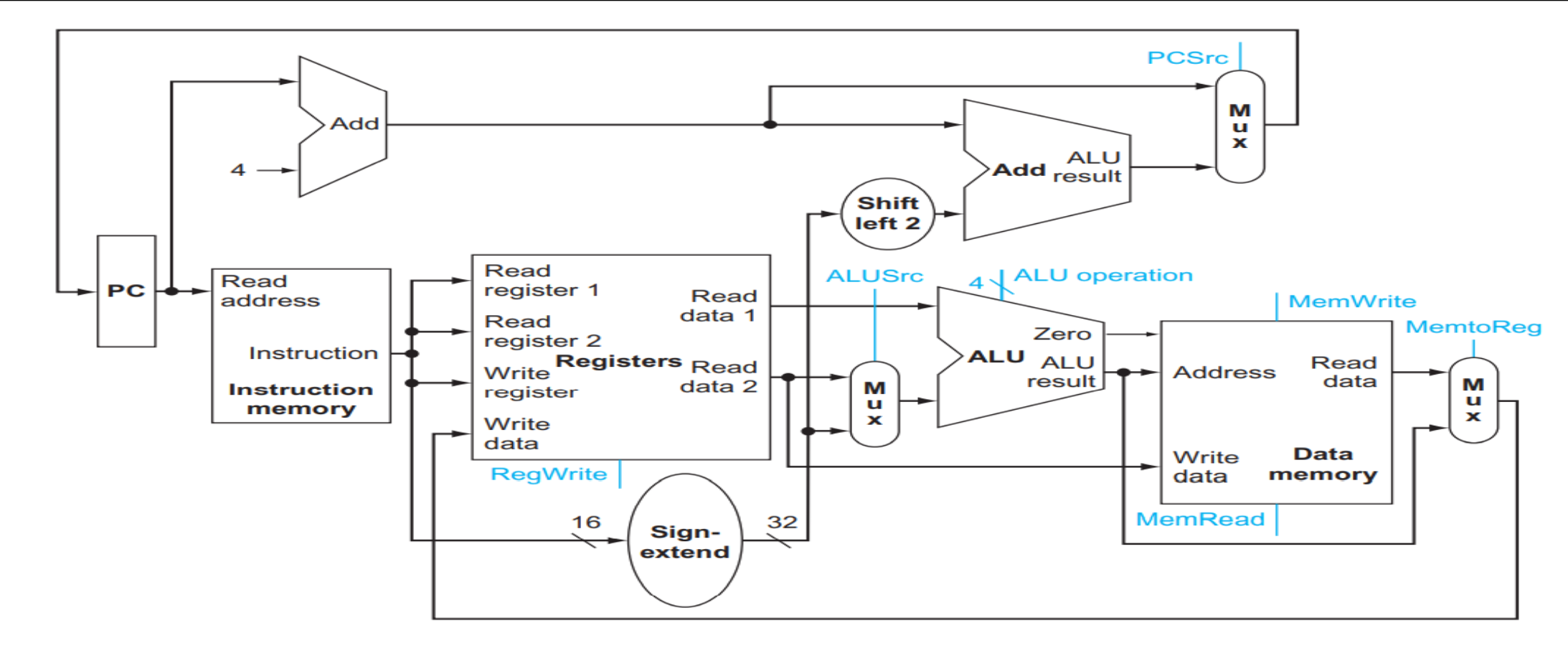

1) instruction을 fetch하기 위해선 PC, Instruction memory, Adder가 필요하다.

2) R-type instruction을 실행하기 위해서는 register file과 ALU가 필요하다.

3) lw/sw instruction를 실행하기 위해서는 register file과 ALU, Sign Extension Unit, Data memory가 필요하다.

4) branch instruction을 실행하기 위해서는 register file, ALU, Sign Extension Unit, Shift left 2, Adder가 필요하다.

위 회로에 beq $t1 3($t2) 가 입력됐다고 가정하자 (PC의 출력이 beq $t1 3($t2)인 것이다.)

우선, PC는 출력했으므로 현재 명령어 위치를 Adder의 입력으로 받아 4가 더해진 값이 PCSrc와 연결된 Mux의 0번째 자리에 들어간다. 또, 추후 offset_value와 더해질 Adder의 입력으로 들어간다.

그리고 offset_value인 3은 Sign Extension Unit로 32bit로 변환되고 Shift left 2 회로로 4가 곱해진 뒤 Adder의 입력으로 들어간다. 그렇게 PC+4와 offset_value*4는 더해져 대상주소가 되고, 이는 PCSrc와 연결된 Mux의 1번째 자리에 들어간다.

$t1과 $t2는 Registers의 입력으로 들어가고, 그의 데이터가 출력된다. 출력된 데이터는 ALU의 입력으로 들어가고, subtract 연산을 수행한다. 이때 Zero flag가 활성화되면 둘은 같은 것이므로 PCSrc는 1이 되고 PC에는 대상 주소가 입력된다.

활성화되지 않는다면 branch가 실패한 것이므로 PCSrc가 0이 되어 PC에는 PC+4가 입력된다.

'학교강의필기장 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조[13]: Control Unit, Jump (0) | 2023.04.16 |

|---|---|

| 컴퓨터구조[12]: ALU Control Unit, Signal 정리 (0) | 2023.04.12 |

| 컴퓨터구조[10]: Datapath, Datapath Elements (0) | 2023.04.09 |

| 컴퓨터구조[9]: MIPS 구조 요약 (0) | 2023.04.09 |

| 컴퓨터구조[8]: address mode - PC-relative / Pseudo-direct (0) | 2023.04.09 |