현생/임베디드

ARM Cortex-M3 Processor Datasheet - 특징 정리

푸더기

2024. 8. 11. 15:00

반응형

개요

원본파일은 여기를 눌러서 받을 수 있다. 데이터시트는 제품의 성능, 기능, 사양, 사용 방법 등을 요약하여 설명한 기술 문서이다.

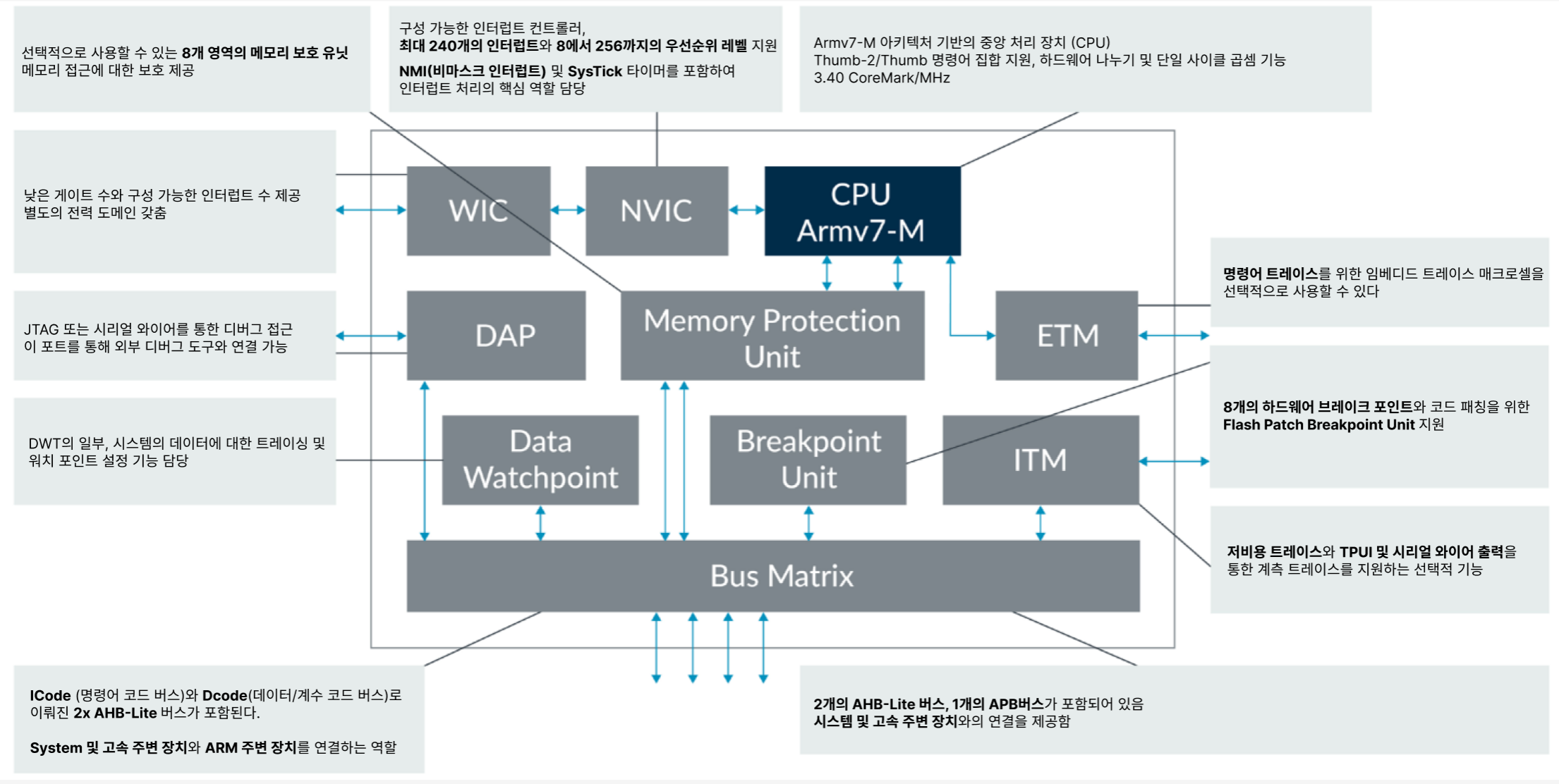

ARM Cortex-M3 프로세서는 높은 성능과 저비용을 목표로 설계된 프로세서이다. MCU, 자동차 바디 시스템, 산업 제어 시스템, 무선 네트워크 및 센서 등 다양한 장치에서 사용할 수 있도록 설계되었다.

주요 특징

| 아키텍처 | Armv7-M 아키텍처 기반 |

| 버스 인터페이스 | - 3개의 AMBA AHB-Lite 인터페이스 (Harvard 버스 아키텍처) - CoreSight 디버그 컴포넌트 위한 AMBA ATB 인터페이스 |

| ISA 지원 | Thumb/Thumb-2 서브셋 지원 |

| 파이프라인 | 3단계의 파이프라인 구조 |

| 메모리 보호 | 8개의 영역, 서브 영역, 백그라운드 영역 포함하는 선택적 메모리 보호 유닛 (MPU) |

| 비트 조작 | 통합된 비트 필드 처리 명령 & 버스 레벨 비트 밴딩 |

| 인터럽트 | 비마스크 인터럽트(NMI)와 최대 240개의 물리적 인터럽트 지원 |

| 인터럽트 우선순위 레벨 | 8에서 256까지의 우선순위 레벨 |

| 웨이크업 인터럽트 컨트롤러 | 선택적 기능 |

| 명령어 확장 | 2-12 사이클에서의 Hardware Divide 명령어 (SDIV, UDIV) 32x32 단일 사이클에서의 Multiply 포화 조정 지원 |

| 슬립 모드 | 통합된 WFI 및 WFE 명령어, 슬립 온 엑싯 가능 슬립 및 딥슬립 신호 Arm 전력 관리 키트를 포함한 선택적 유지 모드 |

| 디버그 | 선택적 JTAG 및 시리얼 와이드 디버그 포트 최대 8개의 브레이크 포인트와 4개의 와치 포인트 지원 |

| 트레이스 | 선택적 명령어 트레이스(ETM), 데이터 트레이스(DWT), 계측 트레이스(ITM) 지원 |

NVIC(Nested Vectored Interrupt Controleer)로, 프로세서 코어와 밀접하게 통합돼 낮은 지연 시간의 인터럽트 처리가 가능하다.

선택적으로 브레이크 포인트와 코드 배치를 구현할 수 있고, 와치 포인트, 트레이싱, 시스템 프로파일링 등 또한 구현 가능하며 printf 스타일의 디버깅을 지원한다.

외부 인터페이스로는, 메모리 및 장치 버스 인터페이스, ETM 인터페이스, Trace 포트 인터페이스, Debug 포트 인터페이스가 있다.

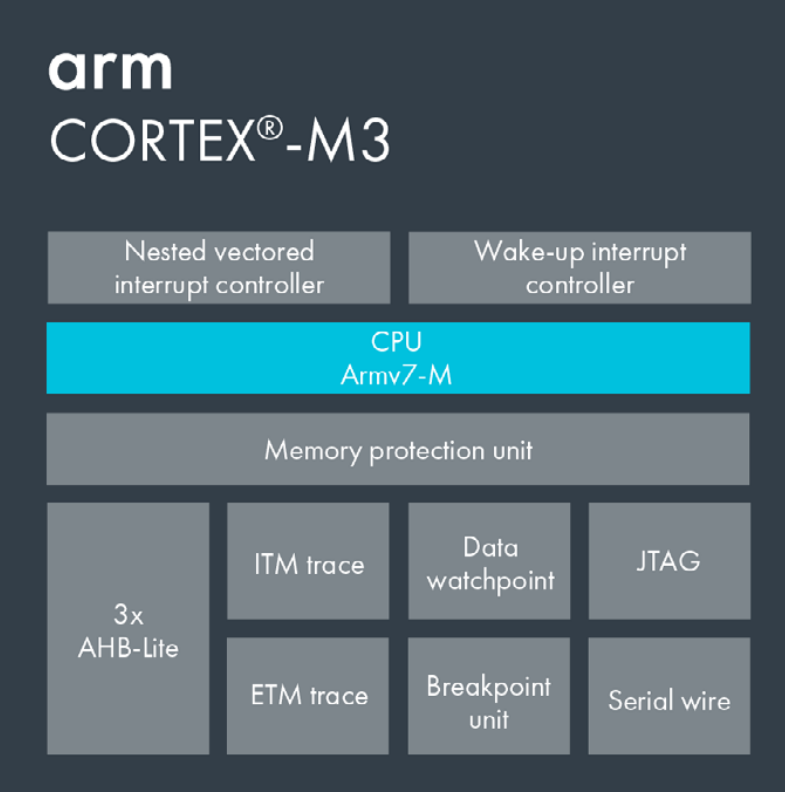

Block Diagram

반응형